**DESIGN DOCUMENT**

# Client - Professor Alexander Stoytchev

# Team 31 - Curriculum for the i281e

Team Members Ethan Uhrich - Team Lead & Treasurer Ariana Dirksen - Editor & Note Taker Tessa Morgan - Task Manager & Webmaster Gigi Harrabi - Client Interaction & Outreach Coordinator

> Contact - sdmay25-31@iastate.edu Website - <u>https://sdmay25-31.sd.ece.iastate.edu/</u> Revised: 12/6/2024 V1

# **Executive Summary**

Our project aims to create a series of labs to act as a curriculum for undergraduate engineering students. The goal of these labs is to introduce students to digital circuits and microprocessors. They are expected to bridge the gap between embedded systems, electronic circuits and digital logic. This will help students better understand how the logic is implemented in hardware and how the software interacts with the hardware. Our design must support hardware focused labs, software focused labs and labs that tie both together. Our design will create reusable testing circuits and programs to allow students to verify their work on the labs. Furthermore, our design must allow students to complete the labs within three hours. With these considerations in mind we focus on hardware labs first then transition to labs that tie software into the hardware and wrap up with software focused labs. Throughout the labs students will use breadboards, microchips, circuit components such as resistors, LEDs, capacitors and wires, ribbon cables and EEPROM memory to implement the various components in the hardware labs. For the software labs students will utilize the EEPROM memory and the i281 simulator to visualize their programs and complete software labs. As these labs build on each other through implementing components of the i281e processor, students can visualize how the various components in the processor work together. So far, we have created four labs, have concepts and basic designs for an additional seven and concepts for two projects for students to complete. Of our created labs two have been thoroughly tested and can be completed in an hour. Additionally, after testing another was found to be too time consuming to be a standalone lab and was broken down into two labs. As much of our testing is reliant on the time it takes to complete the labs and user experience going through the lab we need to test the labs with a focus group. Alongside that we need to finish creating the rest of our labs and iron out more details for the projects. Lastly, we also plan to build at least one additional PCB implementation of the CPU and will ideally also create one to two outreach activities at the middle and high school level.

# Learning Summary

## **Development Standards & Practices Used**

For standard circuit practices we maintained implementation standardization across our hardware and followed a uniform procedure in our documentation and lab manuals. We also use the following engineering standards for this project.

- IEEE 610.10-1994

- IEEE 610.13-1993

- IEEE 1515-2000

## **Summary of Requirements**

- Undergraduate students must be able to complete labs in three hours.

- Labs must be at an appropriate level of difficulty for undergraduate students.

- Lab instructions must clearly communicate all information needed to complete the lab.

- Hardware lab implementations of the i281e components must remain compatible with the PCB implementation.

- Labs must be easy for the students to test and verify the accuracy of their implementations.

### Applicable Courses from Iowa State University Curriculum

| Courses                                                        |

|----------------------------------------------------------------|

| EE 201: Electric Circuits                                      |

| EE 230: Electronic Circuits and Systems                        |

| CprE 281: Digital Logic                                        |

| CprE 288: Embedded Systems                                     |

| CprE 381: Computer Organization and Assembly Level Programming |

Table 1 - Applicable courses for the Curriculum for the i281e Processor project

## **Acquired Skills**

The team has learned many new skills while working on designing and implementing our project. Members of the team have learned how to enforce standardization practices, draw schematics in KiCad and create simulations in TinkerCAD.

# Table of Contents

| 1. Introduction                                                    | 8  |

|--------------------------------------------------------------------|----|

| 1.1. Problem Statement                                             | 8  |

| 1.2. Intended Users                                                | 8  |

| 2. Requirements, Constraints, And Standards                        | 9  |

| 2.1. Requirements & Constraints                                    | 9  |

| 2.1.1. Physical Requirements                                       | 9  |

| 2.1.2. Functional Requirements                                     | 9  |

| 2.1.3. Resource Requirements                                       | 9  |

| 2.1.4. Requirements for Outreach Events                            | 10 |

| 2.1.5. Additional Requirements and Constraints                     | 10 |

| 2.2. Engineering Standards                                         | 11 |

| 3. Project Plan                                                    | 12 |

| 3.1. Project Management/Tracking Procedures                        | 12 |

| 3.2. Task Decomposition                                            | 12 |

| 3.3. Project Proposed Milestones, Metrics, and Evaluation Criteria | 12 |

| 3.4. Project Timeline/Schedule                                     | 13 |

| 3.5. Risks and Risk Management/Mitigation                          | 14 |

| 3.6. Personnel Effort Requirements                                 | 15 |

| 3.7. Other Resource Requirements                                   | 16 |

| 4. Design                                                          | 17 |

| 4.1. Design Context                                                | 17 |

| 4.1.1. Broader Context                                             | 17 |

| 4.1.2. Prior Work/Solutions                                        | 18 |

| 4.1.3. Technical Complexity                                        | 18 |

| 4.2. Design Exploration                                            | 19 |

| 4.2.1. Design Decisions                                            | 19 |

| 4.2.2. Ideation                                                    | 19 |

| 4.2.3. Decision-Making and Trade-Off                               | 19 |

| 4.3. Proposed Design                                               | 20 |

| 4.3.1. Overview                                                    | 20 |

| 4.3.2. Detailed Design and Visuals                                 | 20 |

| 4.3.3. Functionality                                               | 20 |

| 4.3.4. Areas of Concern and Development                   | 21 |

|-----------------------------------------------------------|----|

| 4.4. Technology Considerations                            | 21 |

| 4.5. Design Analysis                                      | 22 |

| 5. Testing                                                | 23 |

| 5.1. Unit Testing                                         | 23 |

| 5.2. Interface Testing                                    | 24 |

| 5.3. Integration Testing                                  | 24 |

| 5.4. System Testing                                       | 24 |

| 5.5. Regression Testing                                   | 24 |

| 5.6. Acceptance Testing                                   | 24 |

| 5.7. Results                                              | 24 |

| 6. Implementation                                         | 26 |

| 6.1. Implementation Process                               | 26 |

| 6.2. Drafting Labs                                        | 27 |

| 6.3. Current Progress                                     | 28 |

| 7. Ethics and Professional Responsibility                 | 31 |

| 7.1. Areas of Professional Responsibility/Codes of Ethics | 31 |

| 7.2. Four Principles                                      | 32 |

| 7.3. Virtues                                              | 33 |

| 8. Closing Material                                       | 35 |

| 8.1. Conclusion                                           | 35 |

| 8.2. References                                           | 36 |

| 8.3. Appendices                                           | 37 |

| 8.3.1. Research                                           | 37 |

| 9. Team                                                   | 39 |

| 9.1. Team Members                                         | 39 |

| 9.2. Required Skill Sets for Your Project                 | 39 |

| 9.3. Skill Sets covered by the Team                       | 40 |

| 9.4. Project Management Style Adopted by the team         | 40 |

| 9.5. Initial Project Management Roles                     | 40 |

| 9.6. Team Contract                                        | 41 |

# List of Tables

| Table 1 - Applicable courses for the Curriculum for the i281e Processor project | 3  |

|---------------------------------------------------------------------------------|----|

| Table 2 - Resource Requirements.                                                | 10 |

| Table 3 - Personal Effort Requirements by Task Breakdown                        | 15 |

| Table 4 - Design Considerations                                                 | 18 |

| Table 5 - Professional Area of Responsibility                                   | 31 |

| Table 6 - Four Principles                                                       | 32 |

| Table 7 - Virtues and Improvements within the Team                              | 34 |

| Table 8 - Product Research                                                      | 38 |

| Table 9 - Skills Needed for the Project                                         | 39 |

| Table 10 - Skills Covered by the Team                                           | 40 |

# List of Figures

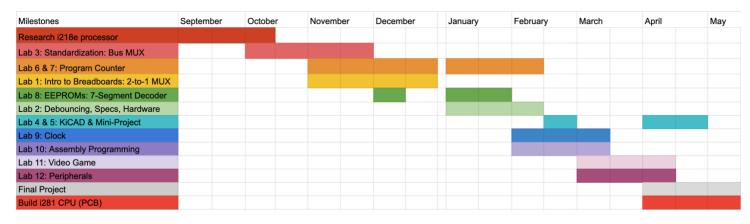

| Figure 1 - Gantt Chart                                                 | 14 |

|------------------------------------------------------------------------|----|

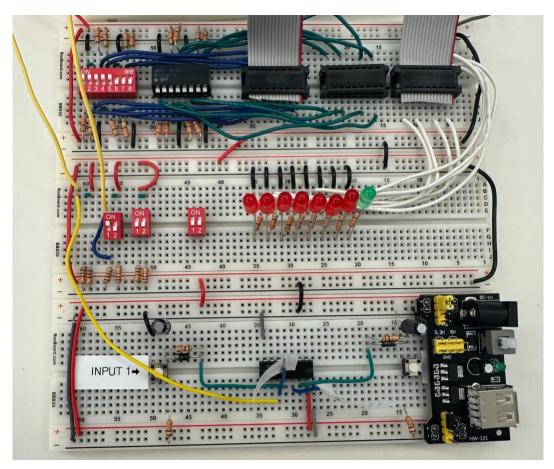

| Figure 2 - Breadboard Mockup of Test board Connected to PC Circuit     | 23 |

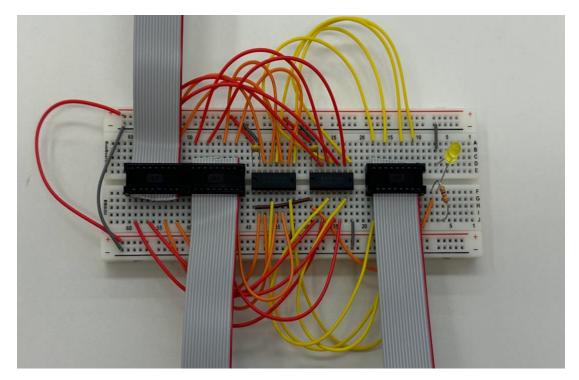

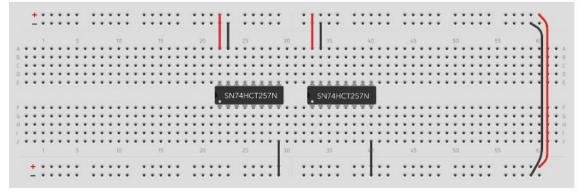

| Figure 3 - Initial Implementation Lab 3's 2-to-1 8-bit Bus Multiplexer | 26 |

| Figure 4 - Beginning of Lab Manual Template                            | 27 |

| Figure 5 - First Section of Lab 1 Report Template                      | 28 |

| Figure 6 - Excerpt from Lab 3 Manual                                   | 29 |

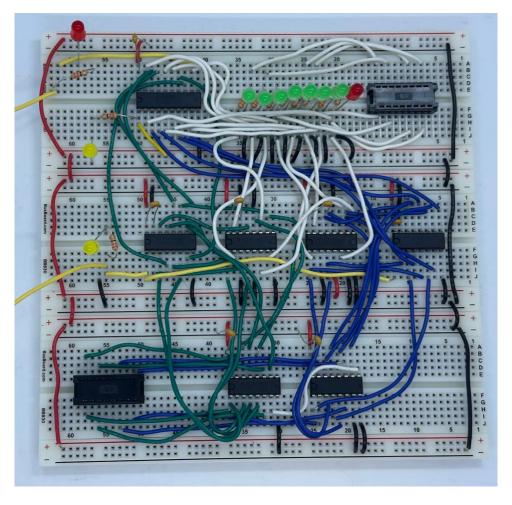

| Figure 7 - Lab 5 & 6 Implementation                                    | 30 |

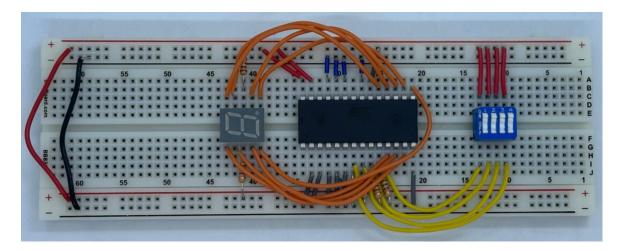

| Figure 8 - Beginning of Lab 7 Implementation                           | 30 |

# 1. Introduction

#### 1.1. PROBLEM STATEMENT

The goal of this project is to use open-source hardware and software designs for the existing central processing unit (CPU), operating system (OS), and simulator to implement a set of lab and outreach activities around the i281e processor. The i218e is a processor built completely on the basic logic that makes processors operate. This processor is a minimalistic design intended specifically as a teaching tool for the department.

These labs and activities will help students who have not used the processor adapt to and learn about how to create and work with processors like i281e. Each activity will be an appropriate complexity such that it can be completed by an average undergraduate student in a reasonable amount of time. Each must be tested by the team and documented with detailed step-by-step documentation. For some tasks, video tutorials could be used as well.

The results will be used to support and enhance the curriculum in Computer Engineering and Electrical Engineering. These documents could also be used as educational materials for existing classes or to support future lectures and labs. A subset of these materials will be used for outreach activities to get the next generation of engineers excited about computers. Part of this project is also to acquire parts for, assemble, and test several new i281e machines. This process must also be documented to aid students and teaching assistants in building these machines for future use as well as potential hobbyists.

#### 1.2. INTENDED USERS

Our project's main users are students who are interested in embedded systems, but who are either in middle/high school or undergraduates in college. Our second type of users are the TAs who may need the materials (lab documents and equipment) who need to conduct the lab or activity to the students. Our final user is the professor who will have a finalized version of this course that will bridge the gap between digital logic, embedded systems, and computer architecture.

Our users' needs are different for each user. For example, the students need to understand simpler concepts of digital logic and embedded systems so that they can understand what is going on in the lab that they are executing. The needs for TA's are a well-written lab document, a rough outline of the answer key and instructions for how to debug once a student is stuck. The professor's need is for the activities to fill in the knowledge gaps that students must succeed in future courses.

# 2. Requirements, Constraints, And Standards

#### 2.1. REQUIREMENTS & CONSTRAINTS

Our requirements include physical, functional, and resource requirements.

#### 2.1.1. Physical Requirements

Our team needs to create at least 10 interactive lab-based activities for the students engaging in the lab events. The labs consist of breadboards, wires, buses, chips and LEDs which are sourced from ETG. As well as software, which is free to use, or custom made for the Labs.

#### 2.1.2. Functional Requirements

The labs need to be within the 2- to 3-hour time limit and feasible for undergraduate students to complete.

#### 2.1.3. Resource Requirements

| Req. # | Description                        |  |  |  |  |

|--------|------------------------------------|--|--|--|--|

|        | Lab 1                              |  |  |  |  |

| 1      | CD74HC08E Chip                     |  |  |  |  |

| 2      | CD74HC32E Chip                     |  |  |  |  |

| 3      | CD74HC04E Chip                     |  |  |  |  |

| 4      | 830-pin Breadboard                 |  |  |  |  |

| 5      | Red LED                            |  |  |  |  |

| 6      | 1.0 kΩ resistor x4                 |  |  |  |  |

| 7      | Breadboard Wires                   |  |  |  |  |

|        | Lab 3                              |  |  |  |  |

| 8      | 830-point Breadboard               |  |  |  |  |

| 9      | Quad 2-1 MUX (SN74HCT257N) Chip x2 |  |  |  |  |

| 10     | 0.1 uF Ceramic Capacitor x2        |  |  |  |  |

| 11     | 830-pin Breadboard                 |  |  |  |  |

| 12     | 5mm Yellow LED                     |  |  |  |  |

| 13     | $330 \Omega$ THT Resistor          |  |  |  |  |

| r                    |                                                |  |  |  |  |

|----------------------|------------------------------------------------|--|--|--|--|

| 14                   | Breadboard Wires                               |  |  |  |  |

| 15                   | Flat Cable Plug x3                             |  |  |  |  |

| 16                   | Connector Wires                                |  |  |  |  |

|                      | Lab 5 & 6                                      |  |  |  |  |

| 17                   | CD74HCT283E Chips x4 (Adders)                  |  |  |  |  |

| 18                   | SN74HCT257N Chips x2 (MUXs)                    |  |  |  |  |

| 19                   | SN74HCT273N Chip (Register)                    |  |  |  |  |

| 20                   | 830-pin Breadboards x3                         |  |  |  |  |

| 21                   | Red LED                                        |  |  |  |  |

| 22                   | Green LEDs x7                                  |  |  |  |  |

| 23                   | Yellow LED x2                                  |  |  |  |  |

| 24                   | 0.1 uF Capacitor x7                            |  |  |  |  |

| 25                   | 330 Ω resistor x10                             |  |  |  |  |

| 26                   | Flat Cable Plug x2                             |  |  |  |  |

| 27                   | Connector Wires                                |  |  |  |  |

| Additional Resources |                                                |  |  |  |  |

| 28                   | i281 + i281e Manuals                           |  |  |  |  |

| 29                   | Previous Senior Design Team's Documentation    |  |  |  |  |

| 30                   | Additional Hardware Components for Future Labs |  |  |  |  |

| 31                   | Any Software required for Software Labs        |  |  |  |  |

|                      |                                                |  |  |  |  |

Table 2 - Resource Requirements.

#### 2.1.4. Requirements for Outreach Events

Set up educational events by contacting WiSE, middle schools and high schools in our area. Activities need to be achievable for the participants. Resources required must be prepared in advance.

#### 2.1.5. Additional Requirements and Constraints

Our constraints may affect the users since the resources are limited to ETG and what is provided from DigiKey hardware wise. Software wise, all students are required to use free software that may not have

a wide variety of resources. For quantitative and qualitative requirements, our advisor and TAs of CPRE 371x should grade the labs out of 100 points. Students should successfully complete about at least 80% of the prelab and understand the big picture of the lab so they can be capable of relating the lab material to class material. Students should be able to complete the lab within 3 hours, and anything beyond that may inquire for help from the TAs. With the help of the instructor who is responsible for carrying out the training of the TAs, while TAs are expected to guide the student, the TAs should not give away the answers verbatim or assist a student in committing academic dishonesty. They are required to report any kind of plagiarism and cheating.

#### 2.2. ENGINEERING STANDARDS

Engineering standards are important since some, if not most, engineering products depend on the quality of the user's life. While browsing the IEEE Standards website, there are products that are related to healthcare and life sciences that if they do not follow the IEEE standards and other codes, will affect the user's life negatively.

IEEE Standard Glossary of Hardware Terminology (IEEE 610.10-1994)- Describes official definitions related to computer hardware relating to computer architecture, computing storage, processors and components [5].

IEEE Standard Glossary of Computer Languages (IEEE 610.13-1993)- Describes the names and definitions of computer languages, and their historical significance [6].

IEEE Recommended Practice for Electronic Power Subsystems: Parameter Definitions, Test Conditions, and Test Methods (IEEE 1515-2000)- Describes testing methods for electronic circuits and systems [4].

The first standard relates to the specific terms that will be used in the i281e processor from an educational perspective. Meaning that those terms will be used to describe and teach the participants during the lab activities. The second one is also relevant because in later labs, we will incorporate the use of a computer language on the operating system, for example, and the use of that standard is important. The third one is important because our project involves building breadboard circuits and testing them

Our team agrees on these standards. These are the main three that will apply to our project as the project is intended for internal use within the department rather than commercial use. Additionally, the project is based around a custom design and just needs to fit the CPU, course curriculum, and faculty constraints.

The modifications we intend to make to abide with the IEEE standards are going to be included within the manual and labs. For example, our team can elaborate on the computing and circuit definitions. In addition, we will ensure that IEEE standards for terminology are used in early labs to familiarize students and others with the terminology that will be used throughout all the upcoming labs.

# 3. Project Plan

#### 3.1. PROJECT MANAGEMENT/TRACKING PROCEDURES

Our team employs Agile for our project management style as we are working on at least ten separate labs that will effectively work as our milestones. We work out the requirements for each lab with our client, Professor Stoytchev, then design the software or circuits, order parts, build, test, and document the process. From there, we develop the first lab assignment draft which we present to the client. Our client gives us feedback, mainly including changes to lab flow and diagrams and additions to the pre-lab and background sections. We then repeat the drafting and feedback iterations until the client checks off on the final draft. Lastly, we have students (outside the project) run through the lab to ensure it can be completed reasonably and flag any last points of concern.

For this project, we mainly communicate and track everyday progress through Discord as well as via weekly stand-ups. Additionally, we will track our task management in GitLab for the design and research of heavier labs. The labs that require developing software will be tracked in GitLab and will rely heavily on Git.

#### 3.2. TASK DECOMPOSITION

Due to the nature of our project, the task decomposition is very natural. Broadly, we will have ten separate milestones for each finalized lab. We will order parts, build circuits, write a program, test, and document each lab. Some labs, mainly the later ones, will require more design and a research phase. An example of one such lab is the EPROM labs, as our team has yet to gain experience programming or using EEPROMs. These labs will require research to successfully learn the necessary software, such as XGpro, the programmer software. We will also be writing a program to play rock, paper, scissors on the i281 CPU which will be written in assembly and will require familiarity with the custom assembly commands and the memory and writing limitations of the i281 machine.

#### 3.3. PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

As stated, we have ten clearly defined milestones in the form of completed lab manuals. We will keep track of the time it took us to build the circuits or write the final code for each lab. Using that knowledge, we will tailor each lab to be completed within a 2- to 3-hour lab by undergraduate students, predominantly in their sophomore and junior years. To accurately measure this, we will test our drafted manuals on students to verify they can be completed in an appropriate amount of time. Within some of the more hardware-focused labs, we are also testing our implementations thoroughly to ensure that the logic works the way it is designed to.

Our main evaluation criteria and metrics are based on feedback from students that complete the final labs. We will create a worksheet for students to complete before and after working on the lab to judge this. During the semester, we will have students (who have completed CprE 2810 and are not in senior design) run through completed lab assignments and gather this feedback.

#### 3.4. PROJECT TIMELINE/SCHEDULE

September-October (red): We researched the i281 processor by looking at past documents and lectures provided by our advisors and previous i281e groups.

October-November (pink): Our team built two copies of the MUX, in groups of two since the labs and outreach events are going to be completed in groups of two, tested the MUX and gone through multiple iterations of the documentation process.

November-February (Orange): Our team built two versions of the program counter which have been tested. They require a clock for the register, so we added a debouncer to the testing circuit to accomplish that. The initial materials for the first draft are also created including several diagrams and the visuals for the activity section of the lab. This lab has also been divided into two parts since we started working on it. Going forward, we're going to add to this lab to include hardware debugging activities.

November-December (Yellow): We put together the introduction lab which will walk students through building a 2-to-1 multiplexor which will lead into later labs. This lab has also gone through multiple stages of documentation and is nearly finalized.

December-January (Green): We started the EEPROM lab which includes programming an EEPROM to store the addresses for a 7-segment decoder. We have built the circuit for this and attempted programming the EEPROM and are currently in the testing stages of this lab.

January-February (Light Green): This lab is going to focus on debouncing techniques, basic hardware components such as LEDs and resistors, and reading datasheets.

February-April (Turquoise): This lab will be an introduction to schematics and using KiCAD. We plan to work on this lab during lighter loads throughout the semester which is why it is split in two. This lab will overlap with a mini project in which students build and order parts to make a bus mux on a PCB.

February-March (Blue): This lab will require students to build a clock circuit and will focus on real-time programming and registers.

February-March (Purple): Lab 11 will introduce students to assembly level programming. For this lab we will likely develop a basic program and give students a skeleton code with various challenges to teach them the various commands available with the i281 CPU.

March-April (Lilac): This lab will implement a video game to tie various components of the CPU and previous labs together. The video game will likely be an implementation of rock, paper, scissors using LEDs and 7-segment displays to show the countdown and scores of the game with push buttons as the input.

March-April (Maroon): The peripherals lab exposes students to hooking up peripherals such as joysticks, a printer, a console, or sound output.

April-May (Red and Gray): This final run of the semester will include work on an example final project and building an additional i281 CPU. We have yet to establish the final project, but it may include modifying the ALU, creating another video game, or letting students choose. Even for the open-ended option, we will come up with an example project to tie the rest of our work together and give students something to go from.

Figure 1 - Gantt Chart

#### 3.5. RISKS AND RISK MANAGEMENT/MITIGATION

The most significant risk for our project is that we cannot order the parts we designed for our hardware implementations. The risk factor is relatively high, as we already dealt with this when ordering our first batch of parts. Thus, if this happens again, we will substitute appropriate replacement parts.

Additionally, our project has a risk that our implementation may not work as expected during testing. In this case, we may have to design alternate implementations and restart our progress in a lab. If this happens with a complicated lab, we plan on scrapping unfeasible labs. This may also require us to create new labs not currently included in our project to replace scrapped ones.

The other risk is that the curriculum committee will not approve this course, and our work will not be used. There is little our group can do outside of ensuring we meet department standards and follow the rules set by ETG to ensure the course is picked up. In the meantime, we must focus on making our project as comprehensive as possible and worthwhile as our capstone projects.

#### **3.6.** PERSONNEL EFFORT REQUIREMENTS

Our Labs are created in four stages. First, we design the lab. Then, we implement it using hardware, software, or both. Then, we test any hardware implementations or programs. Then, we document the expected process for the students. Through the course of creating these labs the labs increase in complexity. Some labs, such as Lab 4, require additional research for us to design and implement. Others, like Labs 5 & 6, need more time for documentation as the processes described in the labs are more time-consuming.

Below is a table with the time each lab has taken or is estimated to take. The times listed are cumulative across all members of the team. The design section includes gathering requirements for the overall lab, creating parts lists, ordering components, and deciding on circuit layouts. Implementation consists of building circuits, writing code, and programming components with various software, including later reworking after receiving feedback on previous deployments. Testing consists of all stages of testing circuits, individual components, final testing on students, and gathering feedback from the client. Documentation includes documenting the overall process, assembling lab drafts, generating diagrams/visuals, and taking pictures. This will cover multiple drafts and stages of edit.

| Task                                    | Design     | Implementation | Testing    | Documentation |

|-----------------------------------------|------------|----------------|------------|---------------|

| Lab 1: Intro: MUX                       | 30 minutes | 30 minutes     | 15 minutes | 4 hours       |

| Lab 2: Debouncing and<br>Hardware       | -          |                | 30 minutes | 1 hour        |

| Lab 3: Bus MUX                          | 1 hour     | 3 hours        | 1 hour     | 8 hours       |

| Lab 4: Intro to KiCAD                   | 1 hour     | 3 hours        | 1 hour     | 6 hours       |

| Lab 6 & 7: Program 2 hours<br>Counter   |            | 6 hours        | 9 hours    | 12 hours      |

| Lab 8: EEPROM 30 minutes<br>Programming |            | 2 hours        | 2 Hours    | 6 hours       |

| Lab 9: Clock                            | 1.5 hours  | 5 hours        | 3 hours    | 10+ hours     |

| Lab 10: Assembly                        | 2 hours    | 6 hours        | 4 hours    | 10+ hours     |

| Lab 11: Video Game                      | 3 hours    | 10+ hours      | 4 hours    | 10+ hours     |

| Lab 12: Peripherals                     | 2 hours    | 10 hours       | 6 hours    | 10+ hours     |

| Final Project                           | 3 hours    | 10 hours       | 6 hours    | 15+ hours     |

| Test Circuit                            | 30 minutes | 3 hours        | 4 hours    | 1 hour        |

Table 3 - Personal Effort Requirements by Task Breakdown

#### **3.7.** OTHER RESOURCE REQUIREMENTS

Each lab requires a set component list to complete. The main components we need for our hardwareoriented labs include

- Breadboards

- Assorted Resistors

- Assorted LEDs

- Assorted Wires

- 0.1 uF Ceramic Capacitors

- CD74HCT283E Chips

- SN74HCT273N Chips

- CD74HCT86E Chips

- CD74HCT377E Chips

- CD4078BE Chips

- Ribbon Cable

- EEPROM Programmable Chip

- SRAM Memory

When completing labs, we will also utilize existing materials from the previously compiled GitHub repository containing PCB schematics for each CPU component. We may also reference the physical breadboard implementation to review circuit layouts. In the future, we will also utilize the online simulator for testing.

# 4. Design

#### 4.1. DESIGN CONTEXT

#### 4.1.1. Broader Context

Our team is tasked to take open-source software and implement them into labs. Students who are at around the sophomore or junior level at Iowa State University are the main users who would benefit from the labs. In addition, anyone who may be interested in our software can replicate our labs, with the list of parts provided in our lab reports and step by step instructions. The professor(s) and TAs teaching the CPRE 371x course and outreach coordinators will also benefit from this since they will be provided with the material and the answer keys.

| Area                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Examples                                                                                                                                                                                                                                           |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public health,<br>safety, and<br>welfare | Our stakeholders who are the TAs,<br>professors, and outreach coordinators<br>would likely be concerned about the tools<br>and improvement of teaching<br>effectiveness. For students, the project<br>leads to improved learning outcomes<br>through more engaging and effective<br>teaching methods, as well as increased<br>access to academic resources. This creates<br>a more supportive learning environment<br>that fosters student success.                                                                                                                                                                                                                                    | Students will understand and build the<br>knowledge gap between embedded<br>systems (software and hardware) and<br>computer architecture, which includes<br>a range of basic digital logic to more<br>complex components in a RISC-V<br>processor. |

| Global, cultural,<br>and social          | Our project, a community-based<br>engineering education program, reflects<br>the values and aspirations of the local<br>cultural group by prioritizing community<br>engagement and representation. By<br>involving professors, TAs and receiving<br>feedback from students in the planning<br>process, we ensure that the program<br>aligns with the community's emphasis on<br>education as a means of empowerment.<br>Additionally, by recruiting mentors from<br>similar cultural backgrounds, we provide<br>relatable role models who inspire students<br>to pursue careers in engineering fields,<br>ultimately fostering a sense of pride and<br>ownership within the community. | Students and other interested<br>participants will be capable of<br>accessing our open-source software<br>and replicating the labs to further<br>understand our course.                                                                            |

| Environmental                            | One issue may be the concern of wasting<br>wire connections in electrical kits since<br>they are too short or long. A way to<br>combat this is to customize and cut<br>specific wires with certain measurements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | This method would decrease the use<br>of plastic and decrease disposing<br>unneeded wires.                                                                                                                                                         |

| Feenemie | Our project is at low cost. A singular        | Our recourses that are provided are at  |

|----------|-----------------------------------------------|-----------------------------------------|

| Economic | Our project is at low cost. A singular        | Our resources that are provided are at  |

|          | electrical lab kit costs at least about \$15. | relatively low cost to make those labs  |

|          | But, at outreach events, students can         | but are at no cost to participants who  |

|          | participate at no cost.                       | are willing to learn about the labs.    |

|          |                                               | Individuals who come across our         |

|          |                                               | open-source software will need to       |

|          |                                               | provide their own lab kit. In addition, |

|          |                                               | university students who register to     |

|          |                                               | attend CPRE 371x will be provided       |

|          |                                               | with a prepared lab kit by the          |

|          |                                               | university.                             |

Table 4 - Design Considerations

#### 4.1.2. Prior Work/Solutions

Past teams have worked on the i281 CPU. The teams worked on breadboard implementations [8][10], a simulator implementation [9] and a PCB implementation [8]. The gap our team is filling in is an educational implementation, which is a combination of software and hardware, specifically breadboard implementations. An advantage our team will provide is a further and more detailed understanding of the i281 CPU architecture and develop lab work to benefit whoever wants to understand the i281 CPU. Another advantage is our CPU is unique and there is not as much, if anything, like it on the market.

#### 4.1.3. Technical Complexity

Our project has many moving components and different labs that can utilize these components. The labs consist of a mix of hardware and software labs that cover the various components related to computer architecture, like the ALU, program counter and seven segment display, along with the opportunity to troubleshoot and debug hardware issues of these labs and components. From a design standpoint, our project is made from an educational perspective and one of the many challenges is gauging the level of difficulty of each lab for a variety of audiences ranging from middle school to highschoolers for outreach events, and university students for the CprE 3710x course.

#### 4.2. DESIGN EXPLORATION

#### 4.2.1. Design Decisions

For the first semester, we are focusing on completing four labs. The intro lab which will require a custom circuit to introduce students to breadboards, wiring, and standardizations. The MUX and Program Counter (PC) labs which will implement components used in the actual i281 CPU. Last, we plan to program an EEPROM which will be the first of two EEPROM labs. The second will use the EEPROMs to program a 7-segment display.

The first decision we made was which labs to implement in the first semester. We needed to familiarize ourselves with the CPU so starting with the MUX and PC were easy starting points. In building these on breadboards, especially the PC, we came up with new layouts that will ideally have cleaner wiring for students to more easily build.

In ordering parts, we discovered that the EEPROM (W27C512), used in the existing design, is no longer in production. We came up with a replacement that would meet as many specs as possible and decided on the AT28C64B-15PU which has less storage but is cheaper and maintains an adequate speed unlike other replacement options.

We also came up with a timeline for all ten labs. The first few labs are very hardware-oriented, but the CPU has its own set of assembly instructions, so we needed to make sure to incorporate that. We decided on one of the later labs to implement rock, paper, scissors on the CPU where the inputs will be pushbuttons for each user and a series of LEDs or 7-segment displays.

#### 4.2.2. Ideation

When deciding what labs to do, each of us came up with two ideas. This included an introductory lab, visualizing flip flops, rock paper scissors, memory storage on breadboards, tic tac toe, a maze using joysticks, and nim. Based on these options, we further fleshed out what labs Professor Stoychev had in mind and prioritized the labs based on that. This introduced us to the idea of a couple EEPROM labs. We then decided a good, interactive lab would be rock paper scissors which would be more software heavy to offset the first labs. It can also be visualized using the work done in previous labs including the EEPROM 7-segment display code. With that game in mind, we had most of our labs filled up and planned to continue further fleshing them out.

#### 4.2.3. Decision-Making and Trade-Off

After discussing our lab timeline with the client, it became clear that most of the labs were already scoped out including the introduction lab, a MUX, PC, and ALU labs, two EEPROM labs, device drivers, and a final project. This left us with two labs of our choice including a game, which Professor Stoychev had suggested in the proposal, for which we decided on the rock paper scissors game since it will be straightforward to represent on the CPU and can incorporate the previous 7-segment display lab.

#### 4.3. PROPOSED DESIGN

#### 4.3.1. Overview

Our project consists of implementing 10 interactive labs. It combines material from some of the core computer engineering classes, CprE 2810, CprE 2880, and CprE 3810, and helps students associate the material with physical implementations. The key components of our projects are our circuits, diagrams and lab manual for each activity.

Description of each class:

- 2810: Introduction to digital logic consisting of digital logic gates, making more complicated circuits like flip flops, counters and registers

- 2880: Embedded systems; programming drivers

- 3810: Implementing a RISC-V processor in Verilog which is based off CprE 2810

Each class has a concept implemented in one of the 10 labs. For example, the current working labs are related to mainly 281,381, and a small bit of 288 on the hardware end. The labs that relate to 281 are chips and breadboards, MUX, PC and rock paper scissors lab. The labs that relate to 381 is the ALU lab. The KiCad and EEPROM labs relate to the CprE 2880 class.

#### 4.3.2. Detailed Design and Visuals

The key components of our projects are our circuits, diagrams and lab manual. Our labs consist of the following sections:

- Prelab: Questions for students to answer to place a baseline expected knowledge before they start the lab.

- Objectives: The purpose of this lab.

- Background: This is also related to the prelab, which is what kind of components and concepts will be used in this lab.

- Standardization and Implementation: How this lab will be expected to be implemented and evaluated for the teaching assistants.

- Activity for lab: A description of which topic the class is currently studying to help students understand the material of this class a bit more. Also, a problem statement for what they need to do and which documents and hints they can refer to.

- Steps and Results: Details of the steps needed to complete this lab whether they are calculations, word or picture descriptions. In addition, what the expected outputs would be for the labs.

#### 4.3.3. Functionality

Our design will operate as a series of labs attached to an experimental class that students who are interested in computer engineering can use to attain a better understanding for the previous classes they took if they were to be a college student at Iowa State University. For other students who are not familiar with this, the labs can serve as a basic understanding of computer engineering overall.

#### 4.3.4. Areas of Concern and Development

There are different levels of user satisfaction:

- Basic: A very rough lab draft, testing circuit works, circuit or lab works mostly (70%-80%)

- Moderate: A revised lab draft that may need more iterations, testing circuit works, circuit or lab works mostly (90%-95%)

- Excellent: A revised lab that went through many iterations, testing circuit works, circuit or lab works completely

Primary concerns: Lab draft may not be clear enough for TAs and the professor. In addition, we are concerned that our team may not be able to gauge the success rate of students, as in, the students may find it too difficult to complete the lab, resulting in discouragement.

Questions to professor and TA(s):

What can be considered as a successful lab?

What can our project do to help the students enjoy the lab material but also not overwhelm them with it?

What kind of instructions can we improve to give the students and TAs to help them understand/instruct the lab?

#### 4.4. TECHNOLOGY CONSIDERATIONS

The first main technology used in our design are breadboard circuits. The advantage of using breadboards is that they are very easy to test circuits and designs in an inexpensive and quick way. This allows us to make changes to the original circuit designed for the i281e processor. This also allows us to prototype what we are asking the students in our design to do where we can get an idea for how long a circuit takes to build on a breadboard. The main weaknesses of breadboards is that parts are not soldered in and thus have a tendency to come loose if not handled with care. In addition, parts placed in a breadboard are generally more fragile because of their cheapness and parts can become damaged without an easy way of testing them out. In addition, breadboards themselves can break from time to time and cause issues that way. But we decided to go with breadboards anyway because they provide them with the most accessibility to physically building circuits.

The second technology we are using in our design is KiCad. KiCad allows us to design circuits that could later be printed onto PCBs. The main advantage of using KiCad is that the previous team's designs were made in KiCad so no translation of circuits into a different program needs to be done. In addition, it makes it very easy to see what values of the chip's inputs are and which are outputs. Some weaknesses of KiCad is you can't make the diagram follow which side the pins are on so, in KiCad all inputs are to the left and all outputs to the right. This makes it difficult to visualize how the circuit will look on a breadboard because of this. In addition, the images produced from KiCad are not easy to read the small numbers so sometimes it takes some educated guessing to figure out which pin the diagram meant. Overall, we went with KiCad because of its previous use on the team and possible future lab portions will use KiCad to show PCB design.

The final technology we have used in our design is TinkerCad. TinkerCad is a website that allows us to generate clean images of the breadboard circuit so that wiring that may obstruct the view for those just following the pictures have a clear view on where the circuits connect. As mentioned before the strength of TinkerCad is its clarity in circuit wiring compared to just an image of the circuit. A weakness of TinkerCad is that it doesn't have all the chip layouts we need but we spent some time and custom made them. Overall TinkerCad was chosen because it generates those very clear images that makes the labs as easy to follow as possible.

#### 4.5. DESIGN ANALYSIS

As previously mentioned, we create our lab in stages. These stages are designing the lab, ordering parts for the lab, building the hardware or code the software to mockup the activity for the lab, testing the design for the lab, then finally documenting. Currently, we have Lab 6, the program counter, in the documentation stage. We have Lab 8, the 7-segment decoder using an EEPROM, in the testing stage. And Lab 1, implementing digital logic, along with Lab 3, the bus MUX, are completed.

As it stands our design is currently working as we have not had to scrap a lab yet. We have been able to implement multiple circuits and have a lab that is almost complete. Thus, while we have not tested with any TA's or students our labs seem feasible. But as we only have one lab at the moderate stage of development with three still at the basic stage it's still too early to tell if all our lab topics are plausible. Once we implement more of the labs, we'll be able to decide how to better structure our labs timeline.

For our future state we plan on finishing the labs currently in progress and beginning more labs. This includes more design, implementation and testing with the new labs. As our project is a curriculum of labs, we also plan on further designing the progression of the labs, additional testing materials, such as test circuits or programs, and any additional circuits, programs or interfaces that we find the need to create. Given the promising start with the MUX lab, we believe that we will be able to complete the rest of the labs. Our only hurdle is making sure that we can secure the necessary materials as needed.

# 5. Testing

#### 5.1. UNIT TESTING

For each of our breadboards our main methods of testing include multimeter voltage testing and unit testing with our test board. With multimeter testing we can probe voltages at different points in the circuit to allow for us to check if a component is working as expected.

In addition to multimeter testing, we also test circuits used in labs with a test board. Our test board consists of

- 2 sets of 8-switch dip switches which allow us to provide two 8-bit inputs.

- 3 sets of 2-switch DIP switches which allows for up to 6 various select lines.

- 2 debounced push buttons which allows for a manual clock input.

- 8 LEDs used to display the output of the circuit.

There are plans for next semester to create a PCB of this test board, see figure 2, usable in labs to allow for a sturdier implementation that can stand up to more rough use in a lab setting where a student would just need to plug in their design to the board without having to worry about pin placement.

Figure 2 - Breadboard Mockup of Test board Connected to PC Circuit

#### 5.2. INTERFACE TESTING

The main way of interfacing with our designs is through our labs and through our test board described above in unit testing. The labs are how we are demonstrating our design ability and testing the labs was done through a rigorous editing process and testing with students who may take the class. Future testing may include testing with the board itself. With the testing board we are able to test if the breadboard units designed will interface properly with the i281e processor which is a good way to show that the designs we have created properly interface with the processor.

#### 5.3. INTEGRATION TESTING

The main process of integration testing is ensuring that all the lab materials, components, activities and instructions all function together to achieve the lab's goals. The most critical path is the integration of the breadboard design to instructions. It's important for instructions to be clear and unambiguous so that the lab can be followed and completed within the requirements. This can be tested with rough drafts of labs and run throughs with students to ensure that all the information is being correctly translated to the lab.

#### 5.4. SYSTEM TESTING

For our system testing we are using students around the experience of those who will be doing the labs and having them do the activities and see where improvements or clarifications can be added to the activities and directions. In doing this we are not only getting feedback on the labs from those who would be doing it but ensuring that the labs are of appropriate length and difficulty to fit without our requirements.

#### 5.5. REGRESSION TESTING

We ensure that new labs and breadboard don't break old functionality by following a strict set of standardization when it comes to interfacing between components and following a set guideline when creating labs to make sure that even if different people worked on the same part of a lab that a student wouldn't be able to tell. Most of these standards we are following were laid out by the previous i281e senior design groups.

#### 5.6. ACCEPTANCE TESTING

In the creation of circuits and labs whenever we have a mockup or a draft, we involve the client by having him go over our designs or drafts and leave feedback. With the circuits this mainly involves checking if the placement of the components make sense, if standards are being followed and if the circuit is clean enough to be understood. In terms of the labs our client and us work together in red pen to make changes that the client wants to the lab whether it be adding more sections or making edits. This ensures that the quality of the product is where the client wants it and that all requirements are being met.

#### 5.7. RESULTS

Through one of the tests, we did with a student they were able to complete our MUX lab in 1 hour and 46 min with help from one of our group members who acted like a TA/group partner to them. This

demonstrated that we were falling short of the 2-hour mark of a lab but with setup and cleanup can meet that 2-hour requirement. This helped us clean up some of the wording in our activity for the MUX and get a real timeline on how long an activity like this will take. Our next steps will be to repeat testing with similar students to get a wider range of results and feedback. This will allow us to have the best final product going forward.

# 6. Implementation

#### 6.1. IMPLEMENTATION PROCESS

For our implementation process we are approaching our labs one at a time. First we select and design a lab from our designed curriculum. Then we order the parts needed to implement any hardware components for the lab. Once the parts arrive, we begin implementing our designed activity for the lab. For implementation we work through the activity that the students will be completing in the lab and build any testing components or programs needed. This lets us gauge roughly how long the activity will take to complete. It also informs us of potential challenges students may face if we make the lab according to our initial design.

Figure 3 - Initial Implementation Lab 3's 2-to-1 8-bit Bus Multiplexer

While we work through the activities, we closely monitor any difficulties that we face in completing the activity. Difficulties include unusual results when testing components, problems with IDEs or design programs, designs that do not give us accurate results and things we learn by going through the activity that are helpful for completing it. If the designed activity has any major problems or it does not give us the intended results, we adjust the design to remedy the problems. Once a design is thoroughly tested and all the major and a majority of the minor problems are worked out. We bring the lab before the team and client for approval. Once a lab has been thoroughly tested and approved by both the team and client we begin drafting the first draft of the lab documentation.

#### 6.2. DRAFTING LABS

Each lab features two main and additional supporting documents. The two main documents are the lab manual and the lab report. While supporting documents range from grading rubrics and answer keys to specification sheets and supplemental resources.

Each lab manual features five main sections.

- Lab Objective

- Background

- Activity

- Testing

- Parts List

The contents of the lab reports change depending on the content of the lab. The only part that will always be present is the prelab.

Once the first draft is finished the team consults the client for feedback. After receiving feedback the team makes required, clarifying and formatting changes necessary to the lab. Then the process is repeated until both the team and client are satisfied with the lab.

#### CprE 3710x Lab X Electrical and Computer Engineering Iowa State University

#### 1.0 Objectives

What do we want to accomplish with this lab? What should the students get out of the lab? What does this lab cover?

#### 2.0 Background

What information do the students need to understand before working through the lab? Does this lab require any logic? How does the circuit work? What will the student's find difficult to figure out if it's not included? Subsections might be dedicated to different parts of the lab or included prior to the activity step where the information is needed.

#### 3.0 Activity

What steps do the students need to do to complete the lab? This is where the points are, what do the students need to accomplish to get these points? Offer general guidance, but how much direction is necessary for a student to draw the necessary conclusion on how to complete the activity?

#### 3.1 Specific Activity Step

What is the first step to the overall goal of this lab?

Figure 4 - Beginning of Lab Manual Template

#### 6.3. CURRENT PROGRESS

As a team we have three labs in drafting, and another is in implementation. Our first lab has a finished lab report and a completed first draft.

| CprE 3710x Lab 1<br>Electrical and Computer<br>Engineering<br>Iowa State University | Implement a 2-to-1 MUX |

|-------------------------------------------------------------------------------------|------------------------|

| Name:                                                                               | Student ID:            |

## Lab Section:

Date:

#### Prelab

Complete the truth table for the following Boolean function:  $f = sx_1 + sx_2$

| s | <i>x</i> <sub>1</sub> | <i>x</i> <sub>2</sub> | $\overline{sx}_1$ | sx <sub>2</sub> | f |

|---|-----------------------|-----------------------|-------------------|-----------------|---|

| 0 | 0                     | 0                     |                   |                 |   |

| 0 | 0                     | 1                     |                   |                 |   |

| 0 | 1                     | 0                     |                   |                 |   |

| 0 | 1                     | 1                     |                   |                 |   |

| 1 | 0                     | 0                     |                   |                 |   |

| 1 | 0                     | 1                     |                   |                 |   |

| 1 | 1                     | 0                     |                   |                 |   |

| 1 | 1                     | 1                     |                   |                 |   |

Figure 5 - First Section of Lab 1 Report Template

Lab three has the first draft of the lab report completed and the lab manual is in its fourth revision.

#### 4.0 Activity

Students need to complete the pre-lab to help complete this lab. In addition, they need to understand which pins go where and the rotation of the chips.

#### 4.1 Place the Bus Connectors and Chips

- The connectors should span pins 60-53, 50-43, and 20-13.

- -The Chips should span pins 40-33 and 30-33.

- Next, connect the source and ground lines on the top and bottom of the board and connect the chips to the source and ground as pictured below.

Before continuing to the next step, have your circuit checked by a TA.

Figure 6 - Excerpt from Lab 3 Manual

Lab five has completed implementation and as the activity took more time than we expected we made it into a two-part lab. We are currently working on the first draft. Lab 7 began its implementation as the initial design was finished.

Figure 7 - Lab 5 & 6 Implementation

Figure 8 - Beginning of Lab 7 Implementation

# 7. Ethics and Professional Responsibility

This discussion is with respect to the paper titled "Contextualizing Professionalism in Capstone Projects Using the IDEALS Professional Responsibility Assessment".

#### 7.1. AREAS OF PROFESSIONAL RESPONSIBILITY/CODES OF ETHICS

It's important that we effectively communicate design progress and feasibility to each other as well as the client. Based on this communication, we can further improve our labs and speed up our workflow. Our team upholds ethical standards since our project is an educational one, it is important to follow the IEEE code of ethics and the university's code of ethics by setting a good example for the students who will be taking this course. Our ethics for this project most likely lines up with Benjamin Franklin's virtues. Since, our project is for educational purposes and our team operates on honesty and integrity. In addition, our team is upfront about any potential issues that concerns the i281e processor.

| Area of Responsibility            | Communication Honesty                                                                                                                                                                                                                                   |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Definition                        | Reporting work, truthfully without any form of deception to advisors, professors or any faculty who is supervising the project. In addition, that includes truthfully reporting to the public.                                                          |

| Relevant Item from Code of Ethics | Our team reports truthful work with our project<br>advisor and senior design advisors. If there is a<br>concern in our project, our team would bring<br>attention to that concern right away to find ways to<br>address this issue as soon as possible. |

Table 5 - Professional Area of Responsibility

### 7.2. FOUR PRINCIPLES

|                                       | Beneficence                                                                                                         | Nonmaleficence                                                                                                   | Respect for Autonomy                                                                                                                                                       | Justice                                                                                       |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Public Health,<br>Safety &<br>Welfare | Students will gain<br>experience and learn<br>from our labs                                                         | Students will learn<br>in a safe and well-<br>guided environment<br>by the TAs and<br>professor                  | We must make sure<br>students are able to gain<br>experience rather than<br>just following instructions                                                                    | We need to make a<br>fair grading<br>standard                                                 |

| Global,<br>Cultural &<br>Social       | People from different<br>backgrounds and<br>universities can use our<br>open-source software                        | We need to make<br>sure that our open-<br>source software is<br>safe to use                                      | We need to make sure<br>that our instructions of<br>our open-source software<br>are user-friendly and clear<br>to read for all users                                       | Making sure that<br>our open-source<br>software is not<br>plagiarized                         |

| Environment<br>al                     | What students learn in<br>this course may enable<br>some of them to<br>leverage their careers<br>positively later   | We need to keep in<br>mind that we are<br>using a lot of plastic<br>materials and not<br>use more than<br>needed | We need to make sure<br>that our project does not<br>harm the environment<br>and find optimal methods<br>for better use of our<br>resources without also<br>being wasteful | Make sure the<br>materials we<br>source is from a<br>respectable<br>company and not<br>wasted |

| Economic                              | Students are going to<br>have to pay for<br>materials, we need to<br>make sure what they<br>learn is worth the cost | Make sure students<br>don't pay more than<br>necessary                                                           | Keep in mind the cost<br>burden to the department<br>and individual students                                                                                               | Make sure students<br>pay for what they<br>use                                                |

Table 6 - Four Principles

#### 7.3. VIRTUES

Our team believes that communication honesty, financial responsibility and sustainability are important for many reasons. It is important to report honestly in a timely and professional manner since our attitude towards the project and faculty as a team reflects and may influence how students and participants in the labs treat the classwork and lab work. It is also important to our team to be financially responsible and sustainable since the project is also made for future students and individuals who are interested in replicating those labs.

| Team Member                 | Ethan                                                                                                                                                                         | Ariana                                                                                                                                                                                                  | Tessa                                                                                                                                                                                          | Gigi                                                                                                                                                                                                                                                                               |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtue<br>Demonstrated      | Honesty                                                                                                                                                                       | Clear and Through<br>Documentation                                                                                                                                                                      | Attentiveness                                                                                                                                                                                  | Commitment to Quality                                                                                                                                                                                                                                                              |

| Virtue<br>Importance        | It's important to be<br>honest in reporting so<br>that all team<br>members are working<br>with the same<br>information and that<br>what you say can be<br>trusted to be true. | It's important to<br>clearly and<br>effectively<br>communicate<br>information when<br>it's included in<br>project<br>documentation, so it<br>can be understood<br>by readers.                           | It's important to be<br>responsive to the<br>needs of<br>teammates, the<br>project, and the<br>client and be able to<br>prioritize them and<br>come up with<br>workable solutions<br>to them.  | It's important to have a quality<br>documented lab, and that also<br>means that it is important to<br>have constructed lab work of<br>the same quality to ensure that<br>student(s) comprehend the<br>information being given to<br>them.                                          |

| How was it<br>Demonstrated? | Honest reporting of<br>what was worked on<br>and when.                                                                                                                        | Thoroughly creating<br>documentation for<br>the labs and editing<br>group<br>documentation.                                                                                                             | Working with the<br>client to improve<br>several drafts of a<br>lab and get it to a<br>final state.                                                                                            | Going through detailed and<br>thorough testing of our labs to<br>make sure that the concepts<br>are correctly implemented,<br>along with updating lab<br>documentation whenever there<br>is a change in implementation<br>method.                                                  |

| Virtue to<br>Improve        | Industry                                                                                                                                                                      | Frugality                                                                                                                                                                                               | Cooperativeness                                                                                                                                                                                | Completeness                                                                                                                                                                                                                                                                       |

| Virtue<br>Importance        | It's important to<br>make sure that little<br>time is wasted in<br>meetings and work<br>sessions so those<br>meetings can be as<br>productive as<br>possible.                 | It's important to<br>make sure that<br>components are not<br>wasted to keep<br>costs manageable.<br>It's also important<br>that components<br>are used with care<br>and not recklessly<br>gone through. | It's important to be<br>flexible and open to<br>other teammates'<br>ideas. After<br>communicating our<br>ideas, and those of<br>the client, we need<br>to resolve any<br>creative differences. | It's important to make the lab<br>reports feel more like they are<br>made for an engineering<br>course. It's also important to<br>provide the full, detailed<br>information about what the<br>labs would entail and what the<br>questions are really asking the<br>students to do. |

| Team Member                | Ethan                                                                                                                                                    | Ariana                                                                                         | Tessa                                                                                                                                           | Gigi                                                                                                                                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| How Can it be<br>Improved? | Following the Ganntt<br>chart much closer<br>next semester to<br>make sure all labs get<br>done on time and not<br>to fall behind on what<br>is planned. | By being more<br>careful when using<br>components and not<br>being reckless with<br>materials. | Our ideas for some<br>labs are not<br>completely fleshed<br>out and I sometimes<br>focus too much on<br>how I want the lab<br>timeline to work. | It is important to go through<br>many iterations of the lab<br>documents and involve our<br>advisor and other participants<br>in outreach events to provide<br>input about the instructions<br>made in the labs. |

Table 7 - Virtues and Improvements within the Team

In conclusion, our commitment to honest communication, financial responsibility, and sustainability not only enhances the integrity of our project but also sets a positive example for future students and participants. By incorporating these principles into our work, we aim to create a legacy that encourages responsible practices and fosters a culture of collaboration and respect within the academic community.

## 8. Closing Material

#### 8.1. CONCLUSION

Our project's primary goal is to develop ten interactive labs to help students understand processor design and digital logic. These labs are designed to be completed within a 2- to 3-hour lab period and will be supported by comprehensive materials, including documentation, guides, and potential video tutorials. So far, significant progress has been made in developing these labs, with this first semester focusing on four labs: an introduction to breadboards, the bus MUX, the program counter, and an initial EEPROM lab. These labs provide hands-on experience with hardware and software components, helping students visualize how processor components interact. Other labs, such as an introduction to assembly-level programming and the rock-paper-scissors game, are also in the planning stages.

The project has a secondary goal of assembling and testing additional i281e processors (to the one built by a previous senior design team) and documenting that process for future students, TAs, and hobbyists. Finally, we have a stretch goal to offer outreach activities to middle and high school students to spark interest in computer engineering. We have some existing materials and have investigated these goals to scope them out, but plan to implement them next semester.

To achieve all these goals, we follow a structured approach that breaks down the project into milestones, each corresponding to a finalized lab. The development process is divided into research and prototyping, building and testing, and refining the lab documentation. The focus has initially been on hardware labs and will soon progress to software-focused labs and those that integrate both. Our team will gather continuous feedback from students and advisors to refine the labs and ensure they align with course material, clarity, and usability.

Several constraints have impacted the project's progress. Limited hardware resources and free software tools, which lack advanced features, have been challenges. Additionally, the labs must be designed to fit within a 2- to 3-hour timeframe, which has required tracking time and testing for feasibility. Procuring materials has presented challenges, particularly for more complex labs that require specific components such as EEPROMs and custom assembly programs.